نظرسنجی

دستهها

- پروژه های آماده

- ترجمه تخصصی متون برق

- تدریس دروس

- جزوات آموزشی

- دانلود رایگان پروژه

- معرفی و دانلود کتاب

- انرژی های نو

- الکترونیک قدرت

- عمومی

- تلگرام

- ماشین های الکتریکی

- تئوری جامع ماشین های الکتریکی

- کنترل فازی

- مقالات برق قدرت

- نرم افزار برق قدرت

- متلب

- طراحی مبدل الکترونیک قدرت

- کنترل خطی

- الگوریتم های تکاملی

- سیستم های قدرت

- کنترل مدرن

- شبکه شکل دهی پالس

- سوییچ تایراترون

ابر برجسب

برق قدرت پایان نامه برق پایان نامه پایان نامه برق قدرت همانندجو دیگسایلنت سیستم قدرت توربین بادی dfig میکروگرید ریزشبکه پروژه طراحی مبدل الکترونیک قدرت مبدل سوییچینگ مقاله مهندسی برق شبیه سازی مقاله پروژه الکترونیک قدرت شبیه سازی مقاله برق قدرت معما شبیه سازی توربین بادی طراحی مبدل سوییچینگ دانلود رایگان پایان نامه پایان نامه برق الکترونیک کاهش درصد شباهت پایان نامه کاهش درصد همانندجویی پایان نامه سامانه همانندجویی کاهش همانندجویی مقاله برق قدرت مقاله برق مقاله ISI طراحی PCB استخراج مقاله از پایان نامه همانندجویی مبدل الکترونیک قدرت بیت کوین شبکه قدرت کنترل میکروگرید ثبت پایان نامه شبیه سازی متلب کنترل فازی پایان نامه مخابرات پایان نامه کنترل کرکره برقی کنترل مدرن کنترل تطبیقی متلب انرژی تئوری جامع ماشین الکتریکی پروژه تئوری جامع ماشین الکتریکی انرژی برق شبیه سازی dfig دانلود پایان نامه توربین بادی شبیه سازی برق قدرت انجام پایان نامه برق درایو ترانسفورماتور تاسیسات الکتریکی سوالات مصاحبه آزمون استخدامی ابزار دقیق میکروکنترلر آردوینو پی ال سی پروژه برق تافل طراحی برد مدار چاپی آموزش دیگسایلنت سامانه همانندجو شبیه سازی انرژی خورشیدی انرژی باد شبیه سازی مقاله برق سنسور رله دانلود رایگان ترانس جریان چیستان پنل خورشیدی انجام پایان نامه پایان نامه دیگسایلنت چاپ مقاله کاهش درصد همانندجویی ارز دیجیتال پایان نامه میکروگرید کنترل مهندسی برق قدرت الکتروموتور شبیه سازی با متلب انجام پایان نامه برق قدرت پروژه دیگسایلنت شبیه سازی دیگسایلنت پایان نامه ریزشبکه انرژی نو اینورتر توربین بادی پروژه الکترونیک قدرت 2 پروژه پایان نامه توربین بادی پروژه درس تئوری الکترونیک قدرت برقبرگهها

جدیدترین یادداشتها

همه- دیجیتال تویین Digital Twin

- کاهش کپی بودن متن پایان نامه

- آموزش پارافریز

- کاهش درصد شباهت پایان نامه

- صرفه جویی در هزینه و بهبود عملکرد پنل خورشیدی

- آبگرمکن خورشیدی

- تقویت شبکه های برق تجدیدپذیر با هیدروژن

- نیروگاه بادی فراساحلی

- محصولات حاصل از بازیافت تیغه های توربین بادی

- دما و حرارت بالا برای پنل های خورشیدی

- اهمیت بازیافت پنل خورشیدی

- مصر بزرگترین مزرعه (نیروگاه) بادی خاورمیانه

- انواع توربین های بادی

- پنل های خورشیدی تجاری

- ساختمان سبز، ساختمان انرژی صفر خالص

تقویم

بهمن 1402| ش | ی | د | س | چ | پ | ج |

| 1 | 2 | 3 | 4 | 5 | 6 | |

| 7 | 8 | 9 | 10 | 11 | 12 | 13 |

| 14 | 15 | 16 | 17 | 18 | 19 | 20 |

| 21 | 22 | 23 | 24 | 25 | 26 | 27 |

| 28 | 29 | 30 |

جستجو

مقایسه تفاوت های بین دو زبان Verilog و VHDL

مقایسه بین زبان های VHDL و Verilog HDL

مقدمه

طراحان سخت افزار های الکترونیکی ، رفتار و ساختار یک مجموعه ی دیجیتال را با استفاده از زبان های HDL ( مخفف Hardware Description Language ) توصیف می کنند . زبان های توصیف سخت افزار در حال حاضر شامل سه نوع زبان متفاوت VHDL ، Verilog و System Verilog هستند . این زبان های توصیف سخت افزار با زبان های برنامه نویسی نرم افزاری تفاوت دارند زیرا در آنها از ارتباطات سیگنالی و زمان انتشار سیگنال ها سخن به میان است . در هر یک از سه زبان HDL گفته شده سبک توصیف سخت افزار منحصر به خود را دارند . در زبان VHDL و Verilog پیاده سازی در سطح رجیستری است ( Register Transfer Level ) که یک سطح بالاتر از سطح گیت ( Gate Level ) است . اما زبان SystemVerilog در ادامه مسیر تکامل پیاده سازی سخت افزاری از سطح بالاتری از طراحی سیستم های دیجیتال پشتیبانی می کند که در آن در کنار استفاده از نسخه بهبود یافته Verilog ، برنامه نویسی شی گرا ( Object Oriented ) نیز اضافه شده است .

ویژگی های VHDL در مقابل Verilog

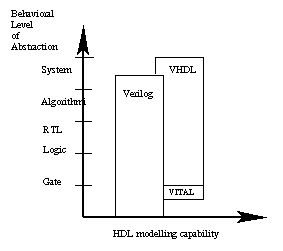

VHDL که مخفف Very High Speed Integrated Circuit Hardware Description Language است از نظر Syntax غنی تر از Verilog است و توانایی مدلسازی سختافزار در بالاترین سطوح انتزاع (تا سطح سیستم) را دارد در حالی که Verilog بیشتر به زبان C شبیه است و از توصیف سخت افزار در سطوح پایین تر طراحی ( سطح گیت ) نیز پشتیبانی می کند . شکل زیر نشاندهنده میزان مقیاس پذیری این دو زبان در سطوح مختلف انتزاع در توصیف رفتاری میباشد .

در زبان VHDL سطح سیستم قابلیتی را ایجاد می کند تا توابع و پروسه ها بتواند در قالب یک پکیج بسته یا Core با Core های دیگر به صورت جداگانه ترکیب شود . یعنی از به هم پیوستن Core های کوچکتر Core های بزرگتر ساخته می شود. اما در Verilog هیچ مفهوم بسته ای وجود ندارد و کلیه توابع و پروسه ها باید در قالب یک ماژول تعریف شود که این ماژول در قالب هدر فایل به برنامه افزوده می شود .

انواع داده در زبان Verilog نسبت به VHDL ساده تر و استفاده از آنها آسانتر میباشد، ضمن اینکه این انواع داده در Verilog به مدلسازی ساختاری نزدیکتر هستند، در این زبان برخلاف VHDL انواع داده مشخصی تعریف شده است و کاربر نمیتواند انواع داده جدید به آن اضافه کند.

برای فردی که پیشزمینهای در مورد زبانهای برنامه

نویسی ندارد، یادگیری زبان Verilogسادهتر از VHDL است، چرا که نوشتن

کدهای VHDL کمی پیچیده تر از Verilogمیباشد و Verilog تقریبا ۵۰ درصد به

زبان C شبیه است .

نمونه یک کد VHDL

reg1: process (rst, cllk)

begin

if rst = ‘1’ then

q_reg <= (others => ‘0’);

q_i <= (others => ‘0’);

elsif rising_edge(clk) then

if s_l = ‘1’ then

q_i(0) <= q_i(7);

loop1: for i in 6 downto 0 loop

q_i(i + 1) <= q_i(i);

end loop loop1;

q_reg <= y;

else

q_i <= q_reg;

q_reg <= y;

end if;

end if;

end process reg1;

نمونه یک کد Verilog

always @(posedge CLK or posedge RST)

begin

if (RST) begin

q_reg = 0;

Q = 0;

end else if (S_L) begin

Q[7:0] = {Q[6:0],Q[7]};

q_reg = Y;

end else begin

Q = q_reg;

q_reg = Y;

end

end